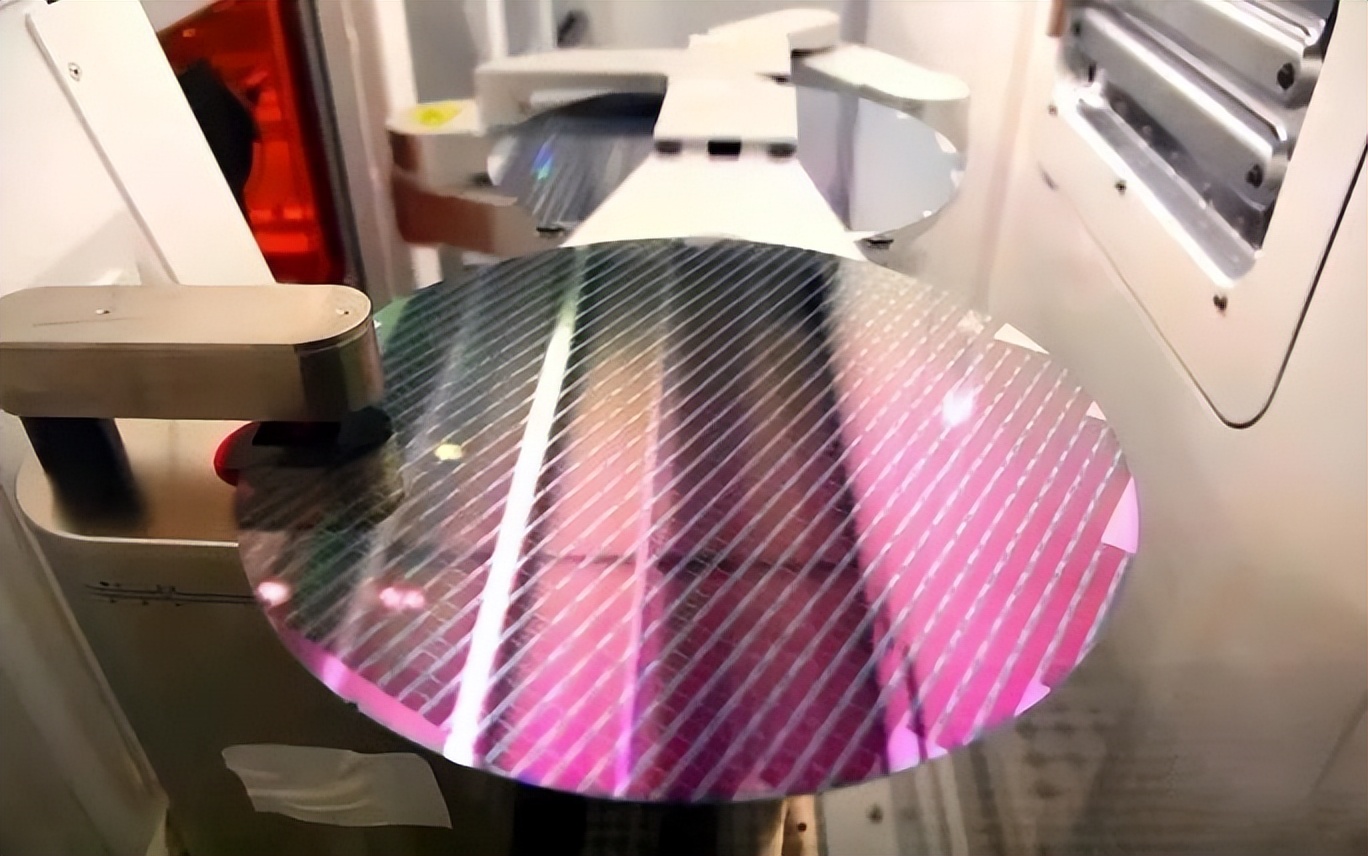

我们知道,芯片都是由晶体管组成的,比如苹果的A16,有160亿个晶体管。而电流在晶体管内部,会从起始端(源极)流向终点(漏极)。

而电流流动过的过程中,会经过一个闸门(栅极),而栅极的宽度正是平时所说的芯片工艺,也就是XXnm,比如苹果A16就是4nm工艺,理论上栅极的宽度就是4nm。

而要提高芯片工艺,比如从4nm到3nm,再从3nm到2nm,就要缩短栅极的宽度。

而栅极的宽度小了,那么源极漏极间的距离就短了。这样造成的后果是源、漏两极的电场对栅极产生干扰,然后栅极对电流的控制能力大大下降,最后芯片不稳定,漏电,功耗增加,性能下降等等……

以前7nm、5nm、3nm时,这种情况还稍能够控制,从而不产生大的影响,但到2nm时,就没法控制了,必须有进一步技术改进才行。

如何在缩短栅极宽度的同时,还减少源、漏两极的电场对栅极的干扰?那就是要改变材料的特性了,使栅极更稳定。

之前台积电等厂商,已经试过很多办法,比如在芯片材料中掺杂磷原子,然后再对这个混合物进行加热退火,提高磷原子平衡浓度,激活活性,提高导电性能。

但目前这项技术也遇到了一些困难,普通的掺杂工艺不行,磷原子的平衡浓度不够高,达不到要求,并且在进行加热退火处理时,还可能会导致晶体管膨胀。

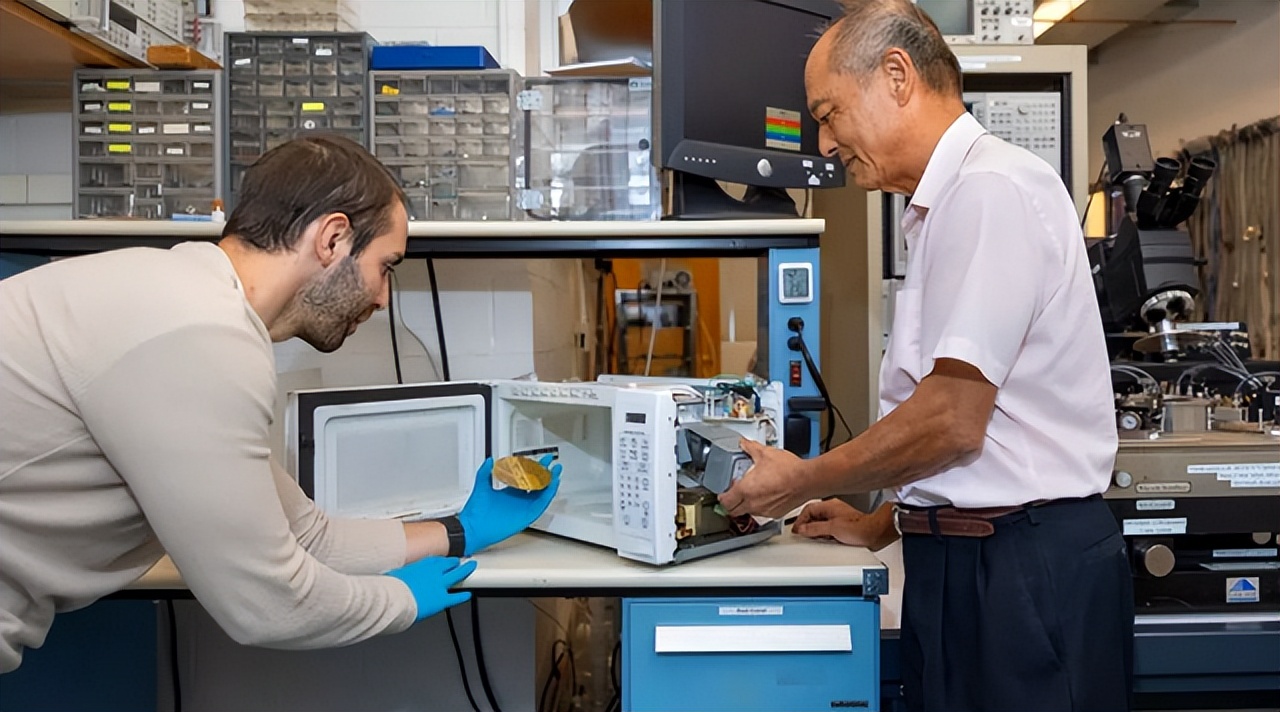

于是近日,康奈尔大学的研究人员提出了一种新的提高磷的平衡浓度的方法:微波技术。

在试验的过程中,研究人员把掺杂磷原子的芯片,放到改进后的家中微波炉中进行测试,发现微波技术,可以使得芯片材料中的掺杂原子被激活,还不会出现晶体管膨胀的状况。

目前康奈尔大学的James Hwang与博士后詹卢卡 · 法比(Gianluca Fabi)共同申请了微波退火器的两项专利,同时相关论文已发表于 Applied Physics Letters。

研究人员预测,这一项技术在2025年就会应用于芯片制造上。

而2025年,台积电、三星的2nm芯片可能就会量产了,所以也就是说,2nm芯片的制造,除了EUV光刻外,可能还需要加一个微波炉了。

微软原文标题!2nm芯片的制造,除了EUV光刻机,还需要一个微波炉?